FPGA Design

Engineering

-

FPGA Design

Concept, Design, Development -

PCB Design

High Speed Digital

RF & Mixed Signal -

DSP

Simulation, Implementation -

Embedded Systems

Linux, Drivers, Scripting -

HMI Development

Qt, GUI, Usability

ARECS offers an end-to-end design services in the field of FPGA design.

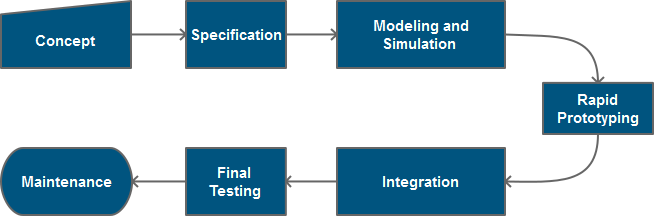

We work with you closely through initial concept phase where the specifications are set. This is followed by the simulation and modeling phase where the design specifications are tested using CAD software.

Once satisfied, we move on to rapid prototyping and implementation phase when the product first sees light. Finally, we conclude by integrating the solution and testing it before handover. We also provide maintenance services.

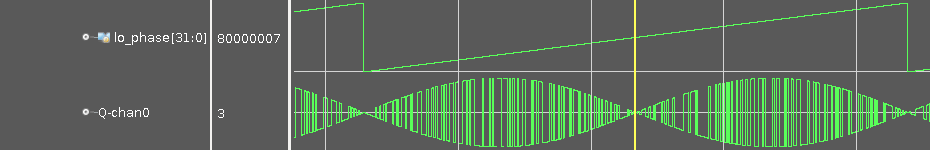

We can also start with your proof-of-concept floating point high level code (MATLAB, C++) and implement it in HDL. We are highly proficient in both VHDL and Verilog on both Xilinx and Altera platforms.

Where applicable, our structured development cycle integrates self-checking test benches for unit testing which accelerates the development cycle. In-house scripts compare both HDL implementation output and intermediate variables against the reference floating point implementation output periodically to catch any potential bugs inadvertently introduced by code updates.

Know how

- Verilog + VHDL

- Xilinx + Altera

- Fixed Point Design

- SERDES Interfacing

- Chip-to-Chip Interconnect